Sản phẩm hỗ trợ đầy đủ tập lệnh mở rộng DSP của RISC-V phiên bản V0. mua thẻ điện thoại 11, bao gồm các phần mở rộng Zpn, Zbpbo và Zpsfoperand, tổng cộng có 244 lệnh đặc biệt được tích hợp nhằm nâng cao hiệu quả xử lý tín hiệu trong các ứng dụng yêu cầu cao.

Hỗ trợ RISC-V N-Trace.

| Đặc điểm | Mô tả | ||||

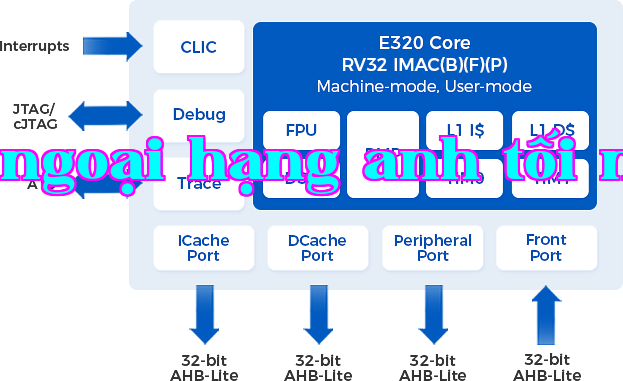

| Kiến trúc tập lệnh | Bộ vi xử lý này tuân thủ theo chuẩn RISC-V 32 bit với các nhóm lệnh IMAC(B)(F)(P)_Zicsr_Zifencei_Zicbom, mang lại khả năng xử lý đa dạng và linh hoạt, đáp ứng tốt cho các ứng dụng phức tạp trong lĩnh vực vi điều khiển và xử lý tín hiệu. | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An toàn | Hỗ trợ Smepmp, có thể chọn 0-16 vùng bảo vệ bộ nhớ vật lý (PMP Region) | ||||

| Giai đoạn xử lý | 3 cấp độ dòng chảy | ||||

| Bộ nhớ trong bộ xử lý | TIM0 và TIM1, kích thước có thể cài đặt (0KB-128MB) | ||||

| Bộ đệm lệnh L1 (L1 I$) | Kích thước có thể cấu hình (4KB-128KB) | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước có thể cấu hình (4KB-128KB) | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 496 yêu cầu ngắt, hỗ trợ ngắt không thể bị bỏ qua (NMI) baobongda | ||||

| Theo dõi gỡ lỗi |

Module gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG

Mô đun theo dõi (Trace module) hỗ trợ N-Trace của RISC-V |

||||

| Giao diện tổng thể |

1. Giao diện bộ nhớ đệm lệnh (ICache Port): Giao diện chủ AHB-Lite 32 bit

2. Giao diện bộ nhớ đệm dữ liệu (Dcache Port): Giao diện chủ AHB-Lite 32 bit 3. Giao diện thiết bị ngoại vi (Peripheral Port): Giao diện chủ AHB-Lite 32 bit 4. Giao diện phía trước (Front Port): Giao diện từ AHB-Lite 32 bit |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.74 | ||||

Số đăng ký mạng xã hội tỉnh Bắc Kinh 11030102011303

Số đăng ký mạng xã hội tỉnh Bắc Kinh 11030102011303